AMD a donné l’une de ces confirmations qui font bouger les choses dans l’industrie : la prochaine génération d’accélérateurs pour l’IA, Instinct MI450sera fabriqué avec Technologie 2 nanomètres. Il l’a dit Lisa Sue dans une interview avec Yahoo Finance et, au-delà du titre, la lecture est claire : l’entreprise veut être compétitive sur le segment le plus difficile du marché, où comptent la densité, l’efficacité par watt et la réelle capacité de produire à grande échelle.

Qu’as-tu confirmé exactement ?

La phrase de Lisa Su était directe et sans fioritures : le MI450 utilisera le nœud 2 nm « le plus avancé » de son partenaire historique TSMC. Ces données correspondent à ce qui a fuité de l’écosystème : une conception hétérogène dans laquelle la combinaison n’est pas capricieuse ; Il vous permet de réserver le nœud très coûteux et complexe à la partie qui s’adapte le mieux aux transistors et de garder sous contrôle le coût et les risques liés aux puces de support.

Pourquoi le passage à 2 nm est important (et quels petits caractères cela apporte)

Passer au 2 nm n’est pas une simple « performance »: implique des performances de fabrication exigeantes, un packaging avancé et un contrôle thermique très fin. L’avantage, si la chaîne d’approvisionnement réagit, réside dans le efficacité par watt et dans la densité de logique qui s’intègre dans le même espace.

Pour l’IA, cela signifie plus de moteurs de calcul, plus de chemins internes et moins de goulots d’étranglement au sein de la puce elle-même. Les petits caractères sont que la fabrication de ces appareils nécessite des interconnexions très denses et un couplage parfait avec les mémoires HBM ; Toute tension dans ces liens ralentit les calendriers.

Mémoire et bande passante : l’arme qui décide des longs jeux

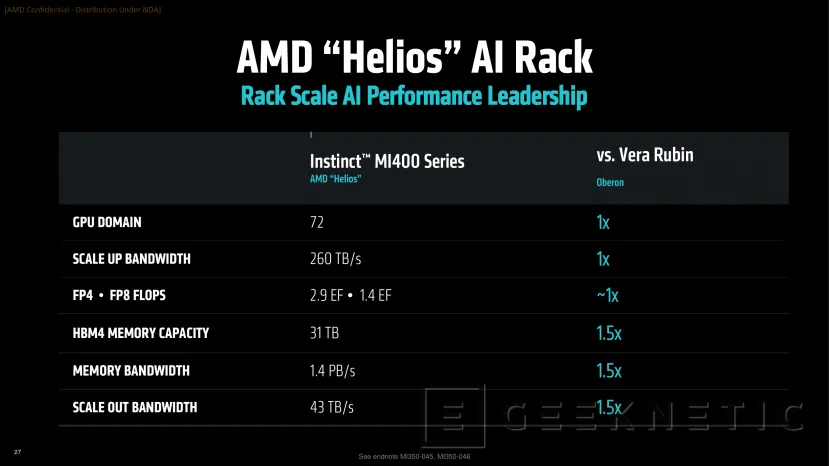

AMD a laissé de côté la promesse selon laquelle elle pourrait effectivement déplacer des contrats : Performances comparables en FP4/FP8 par rapport à son concurrent directmais avec 1,5 fois plus de mémoire et de bande passante. Lors de la formation et du déploiement de grands modèles, ce qui étouffe, ce ne sont pas les téraflops, mais le mur de mémoire. Une plus grande capacité locale et une vitesse d’accès plus rapide signifient moins de déchargement, moins de trafic vers les nœuds voisins et une meilleure mise à l’échelle lorsque le cluster se développe. C’est aussi là que la rumeur bien établie selon laquelle Samsung HBM4 pour MI450: Ce n’est pas confirmé par AMD, mais cela cadrerait avec cette ambition de capacité et de débit.

Le rival de l’autre côté : Rubin, de NVIDIA

La confrontation naturelle sera avec Rubin, la prochaine plateforme de NVIDIA, prévue en N3P (3 nm). Sur le papier, porter le calcul à 2 nm devrait donner à AMD une marge d’efficacité et de densité, mais cette course n’est pas décidée par le nœud seul. Le logiciel, la disponibilité du HBM, la capacité de conditionnement et, surtout, le volume de livraison pèsent en jeu. Même avec cette prudence, si le MI450 tient ses promesses en matière de mémoire et de bande passante, il y aura une réelle pression sur les portefeuilles hyperscale sur lesquels NVIDIA a actuellement un avantage.

Une feuille de route qui aligne CPU et accélérateur

Le mouvement ne se produit pas de manière isolée. AMD prévoit d’utiliser également le 2 nm de TSMC dans la prochaine génération d’EPYC « Venice ». La coordination des cycles entre CPU et accélérateur a du sens pour les opérateurs : elle permet de déployer des pods d’IA avec des pièces conçues pour coexister, avec des profils thermiques et électriques plus prévisibles et avec un chemin de mise à jour cohérent.

Calendrier et attentes raisonnables

Alors que l’année est dans la dernière ligne droite et que SCÉ 2026 jetant un coup d’œil, le scénario le plus probable est une présentation de la série Instinct MI400 en janvier (et peut-être un aperçu officiel de Venise). Introduire ne signifie pas inonder le marché le lendemain : la disponibilité du N2P, l’approvisionnement de HBM et la capacité de conditionnement donneront le véritable rythme. La chose raisonnable à faire est d’attendre des projets pilotes et des déploiements échelonnés avant d’obtenir un volume important.

Quels changements pour ceux qui exploitent des centres de données

Si les éléments s’emboîtent, le MI450 peut fournir un travail plus utile par watt, moins de trafic de données « forcé » en raison du manque de mémoire locale et une plus grande prévisibilité lors de la mise à l’échelle de racks entiers. Que impacte directement le TCO: moins d’énergie à refroidir, moins de nœuds pour un même objectif d’entraînement et moins de temps perdu en réglage défensif. Ce n’est pas une promesse de miracles, c’est la somme de petites efficacités qui, à grande échelle, sont perceptibles.

Ce qu’il manque encore à savoir

Des questions importantes demeurent: la configuration finale HBM (type, capacité par pile, vitesses), l’enveloppe thermique du système complet, les prix et délais de livraison en volume et l’état des bibliothèques et des noyaux pour presser FP4/FP8 dès le premier jour. Ce sont les détails qui séparent une bonne publicité d’un produit qui change d’inertie.

L’Instinct MI450 est la décision d’AMD de rivaliser là où cela fait le plus mal : un nœud de 2 nm en informatique, une mémoire et une bande passante supérieures à la norme, et une architecture qui distribue intelligemment les processus de fabrication. Si la production se poursuit et que le logiciel arrive affiné, 2026 pourrait être l’année où la conversation passera de « qui a plus de FLOPS » à « qui alimente mieux ses accélérateurs ». Et dans cette discussion, AMD s’est placé dans une position qui mérite toute l’attention.