Intel Foundry a publié une courte vidéo ce qui, pour ceux qui suivent l’industrie, fonctionne comme une déclaration d’intention. Il n’enseigne pas une puce commerciale, mais plutôt un concept d’emballage avancé destiné à une époque où les performances ne dépendent plus uniquement du nœud, mais de la façon dont vous connectez d’énormes pièces avec la plus petite pénalité possible.

Le contexte est une limitation physique très spécifique: le réticule du lithographe. En pratique, il existe une taille de référence maximale d’environ 830 millimètres carrés pour une exposition complète. Dans l’IA et le HPC, où l’on essaie de combiner beaucoup de calcul avec une mémoire à large bande passante, ce plafond est devenu un frein.

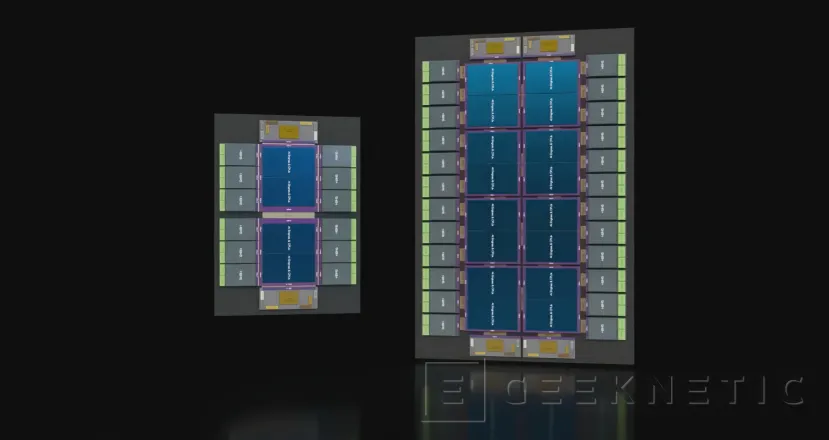

Le message de la vidéo est qu’Intel veut dépasser cette limite sans recourir à un seul gigantesque morceau de silicium.soit. La société affirme que sa combinaison de Foveros 3D et EMIB T peut évoluer jusqu’à l’équivalent de 12 fois un réticule, intégrant jusqu’à 16 matrices de calcul ainsi que 24 modules de mémoire HBM5 dans un seul package, avec prise en charge de HBM4, HBM5 et tout ce qui va suivre.

Il y a aussi une lecture du marché: L’empaquetage avancé est devenu un goulot d’étranglement et TSMC a bâti une grande partie de son avantage en matière d’IA autour de CoWoS. De plus en plus d’analyses mentionnent que certains clients apprécient les alternatives pour ne pas dépendre d’une seule file d’attente de capacité, et c’est là qu’Intel veut entrer avec EMIB et Foveros comme cartes sérieuses.

Au-delà de la grille : une architecture en couches

Ce qu’Intel décrit n’est pas une astuce visuelle, mais plutôt une architecture en couches. La base du boîtier serait fabriquée avec une variante 18A PT qui intègre une alimentation arrière, une technique visant à améliorer la densité logique et la fiabilité en séparant mieux les chemins d’alimentation et de signal. Cette base servirait de fondation, et Intel mentionne des structures SRAM sur le modèle de conceptions internes comme Clearwater Forest.

Sur cette base, les modules informatiques intégrés Nœuds 14A et 14A E, avec transistors RibbonFET de deuxième génération et une stratégie livraison d’énergie appelée PowerDirect. L’idée est que le package ne consiste pas seulement à « assembler des chipsets », mais plutôt à le faire avec des itinéraires électriques conçus pour des charges extrêmes.

Foveros Direct 3D – Empilage avec liaison hybride

La pièce maîtresse de la pile verticale est Foveros Direct 3D. Intel s’appuie sur une liaison hybride cuivre-cuivre avec des pas inférieurs à 10 microns, ce qui augmente la densité d’interconnexion par rapport aux microbosses plus traditionnelles. Avec plus de points de contact et moins de résistance, l’ensemble peut se comporter de manière plus cohérente en termes de latence, de consommation et d’efficacité.

Dans les accélérateurs d’IA, la distance électrique et la qualité de l’interconnexion se traduisent par des performances soutenues. Lorsque la puissance totale augmente, chaque perte en cours de route se traduit en chaleur, et cette chaleur constitue un coût de refroidissement et une limite d’échelle.

EMIB T : ponts de silicium pour la bande passante

Si l’empilement place les pièces les unes sur les autres, elles doivent quand même être jointes horizontalement avec une bande passante maximale. EMIB est l’approche d’Intel pour éviter un interposeur complet: Un pont de silicium intégré au substrat qui relie les chiplets bord à bord. La variante EMIB T ajoute des TSV, des vias via silicium, pour faciliter des liens plus larges et un routage plus flexible dans les gros paquets.

Voici pourquoi Intel insiste sur le support HBM. La mémoire à large bande passante n’est plus un module complémentaire, elle constitue le cœur des accélérateurs modernes. Placer jusqu’à 24 piles HBM5 à côté de 16 tuiles de calcul indique des charges d’entraînement et une inférence massive, où la bande passante est aussi importante que TOPS.

Le GPU de 5 000 watts et le vrai problème : nourrir le monstre

Intel ajoute un chiffre qui semble excessif : un GPU de 5 000 watts avec des régulateurs de tension intégrés au boîtier. L’entreprise le relie à Foveros B, avec l’objectif de préparer la production en 2027. En fin de compte, c’est une manière de reconnaître que la fourniture d’énergie commence à être aussi critique que logique.

Les accélérateurs supérieurs à 2 000 watts sont déjà évoqués dans le secteur, et certaines analyses placent le débat au-delà de 4 000 pour les générations futures. Si la puissance augmente, rapprocher la régulation de la puce, raccourcir les chemins de courant, réduire les pertes et aider à répondre aux pics de charge.

Si Intel parvient à industrialiser cette combinaison de Foveros et EMIB à grande échelle, aura une proposition attractive pour les clients externes qui se tournent aujourd’hui vers TSMC comme référence. TSMC a expliqué comment la taille des interposeurs et des solutions comme CoWoS a augmenté au-delà d’un réseau complet, précisément en raison de la pression de l’IA. Qu’Intel parle de 12 réticules revient, en pratique, à dire qu’il veut jouer au même jeu.

À partir de là, l’élément décisif ne sera pas le rendu ou la silhouette accrocheuse, mais la capacité de répéter le processus, de le livrer avec des performances acceptables et de pérenniser la chaîne d’approvisionnement. Mais la vidéo laisse une idée claire : l’avenir immédiat du silicium se décide à la fois dans le nœud et dans le package et Intel Foundry souhaite participer à cette conversation.