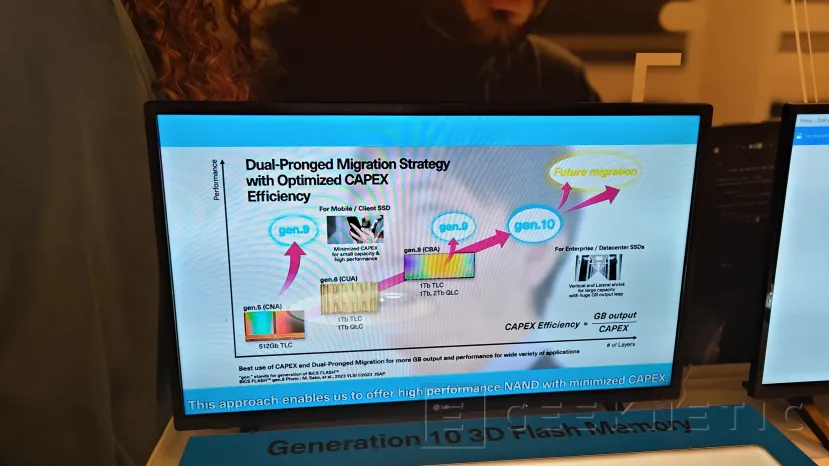

Pour le nouvelle génération de disques SSD, Kioxia continue d’avancer dans la conception de ses cellules mémoire avec une technologie exclusive BiCS FLASH. Le constructeur en a profité SCÉ 2026où en plus de quelques nouvelles également liées au Stockage SSDpour présenter son dixième génération de ce type de mémoire exclusif au constructeur japonais. La dixième génération de 3D BiCS FLASH a 332 couches et technologie CBA cela était déjà présent dans les générations précédentes.

Les nouvelles cellules mémoire 3D FLASH BiCS de Kioxia avec 332 couches

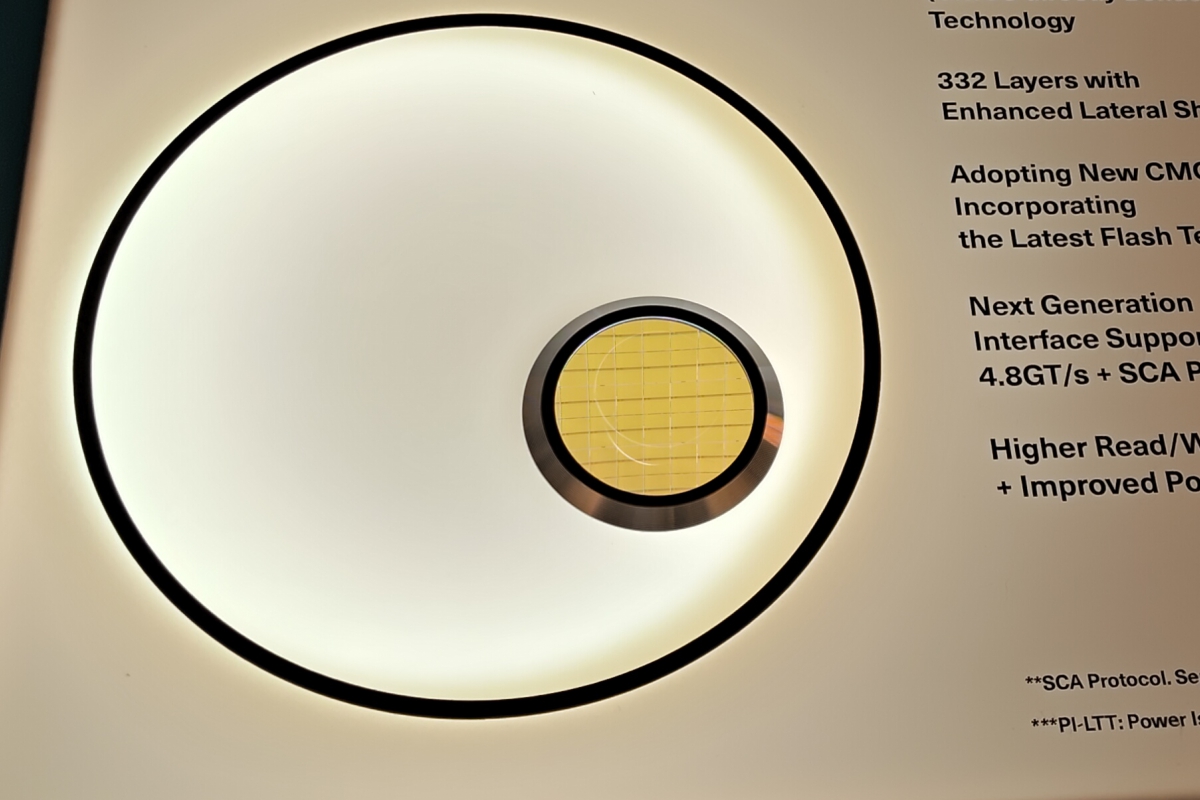

Pour donner vie à la prochaine génération de disques SSD, aussi bien pour les serveurs et les centres de données, que pour les solutions de stockage destinées à la consommation, Kioxia nous montre les avantages de cette dixième génération de mémoires 3D BiCS FLASH. Le fabricant continue de travailler pour ajoutez et améliorez votre technologie CBA (CMOS directement sur la matrice). De plus, cette génération a atteint 332 couches même avec un réduction latérale amélioréeavec un nombre inférieur de couches efficaces par bit.

La 10ème génération de mémoires BiCS FLASH offre jusqu’à 4,8 GT/s

Avec ces mémoires, des disques de nouvelle génération peuvent être construits, car ils offrent jusqu’à 4,8 GT/s pour des performances de lecture et d’écriture plus élevées. Il a aussi meilleure efficacité énergétiquetrès important en ces temps où la moindre consommation favorise ce type de composants. La production de masse devrait commencer dans environ un annous vous laissons le fonctionnalités complètes.

Technologie de fabrication

- Mise à l’échelle avancée avec la technologie CBA (CMOS directement lié à la matrice — CMOS directement attaché à la matrice mémoire)

- 332 couches avec réduction latérale améliorée (Rétrécissement latéral amélioré)

- Utilisation de nouveau CMOS doté de la dernière technologie Flash

Interface nouvelle génération

- Prise en charge de l’interface de nouvelle génération :

- 4,8 GT/s

- Protocole SCA (Protocole d’adresse de commande séparé)

- PI-LTT (Transistor à faible seuil isolé en puissance)

Performance et efficacité

- Performances de lecture et d’écriture supérieures

- Meilleure efficacité énergétique

Objectifs de fabrication

- Réduction de CAPEX (coûts d’investissement de fabrication)

- Moins de couches efficaces par bit grâce à la mise à l’échelle latérale

Notes techniques

- Protocole SCA: protocole qui sépare les adresses de commandes pour améliorer le parallélisme.

- PI-LTT: Transistors à bas seuil avec isolation de puissance pour réduire la consommation.