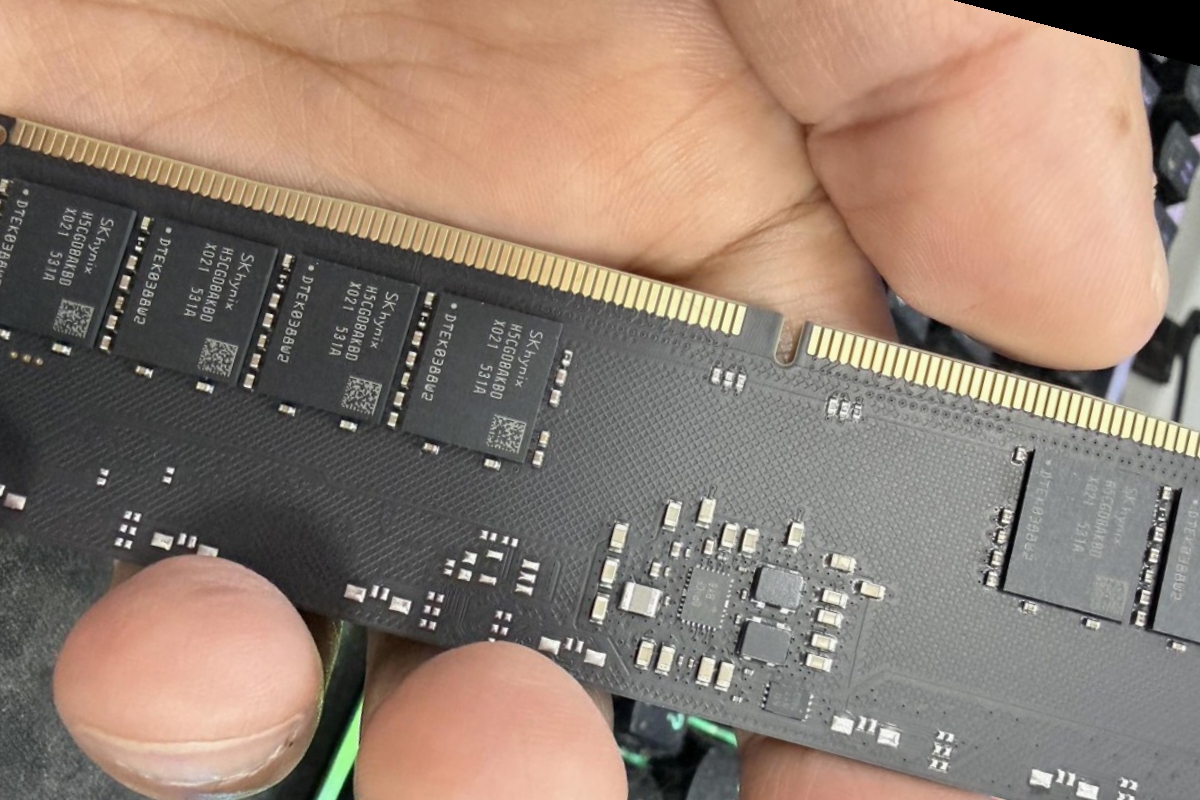

Les fuites avec nom et prénom sont généralement les plus intéressantes car elles permettent de lire entre les lignes. Un module DDR5 avec sérigraphie X021 et code AKBD est apparu sur les photos partagées par Kevin Wu (groupe d’équipe). L’indice qui complète le puzzle est fourni par @unikoshardware : ce serait le nouvelle matrice A de 3 Go de deuxième génération de SK hynix, le successeur naturel du M-die qui dominait la première étape de la DDR5.

De EB à KB : comment lire le « AKBD »

SK hynix a été assez cohérent dans ses labels internes. Les terminaisons EB, FB, GB ou HB marquent des pas en fréquence native JEDEC : 4 800, 5 600, 6 000/6 200 et 6 400 MT/s, respectivement. Si la nouvelle puce ressemble à « KB », l’interprétation la plus raisonnable est 7 200 MT/s de base. Il ne s’agit pas d’un profil XMP/EXPO artificiellement élevé, mais plutôt d’une indication de ce que le silicium peut supporter dans le cadre des spécifications standard, à des tensions et des timings conservateurs.

Densité de 3 Go par puce : ce que cela signifie pour la capacité

qu’on en parle 3 Go par circuit intégré Ce n’est pas un caprice : cela conditionne la topologie des modules. En DDR5, les habituels sont 2 Go et 4 Go. À 3 Go, un DIMM à 16 puces offre 48 Go ; avec 8 puces, 24 Go. Cela correspond à la montée en puissance des kits 2×24 Go (48 Go) et 2×48 Go (96 Go) que l’on a déjà pu constater avec M-die.offrant un juste équilibre entre capacité et latence par rapport au populiste 2×32 Go. Si la nouvelle filière A hérite du bon comportement de la filière M à densités intermédiaires, nous avons pu voir des kits 2 × 24 Go à 7 200-7 600 MT/s stables avec des profils raisonnables sans avoir besoin d’escalades de tension agressives.

PCB 8 couches dans l’échantillon : un plafond pour l’overclocking… et un message au marché

L’unité qui a fui monte un PCB à 8 couches. C’est suffisant pour atteindre 7 200 MT/s JEDEC et des profils un peu plus gais, mais ce n’est pas le terrain idéal pour un overclocking extrême au-dessus de 8 000 MT/s. Pour ce faire, les fabricants passent généralement à 10 ou 12 couches, ce qui améliore l’intégrité du signal, la diaphonie entre les lignes et la distribution de puissance du PMIC.

La DDR5 a appris au fil des itérations que plus de MHz ne signifie pas toujours une meilleure latence efficace. La clé réside dans les tRFC, tFAW, tRCD et tCCD_L que les profils XMP/EXPO définissent pour correspondre à la fréquence et à la stabilité. Les matrices M ont déjà démontré qu’elles pouvaient supporter les CL34-36 entre 7 200 et 7 600 avec 1,35-1,40 V dans des kits bien rangés. Si l’AKBD A-die évolue de manière égale ou meilleure, nous verrons 7 200 profils JEDEC avec des timings assouplis pour une compatibilité universelle et, en parallèle, des profils XMP avec des latences plus agressives dans les gammes passionnées.

PMIC, températures et l’autre moitié des performances

La stabilité d’un module DDR5 ne dépend plus uniquement du circuit intégré ; le PMIC on-DIMM et le système thermique (évier, pads, airflow) jouent un rôle tout aussi déterminant. Entre 7 200 et 7 800 MT/s, le PMIC fonctionne avec des transitoires de courant plus exigeants ; Si SK hynix a optimisé les courbes de consommation de la puce A, les modules seront capables de maintenir des fréquences élevées pendant des charges soutenues sans « limitation thermique » silencieuse. Ainsi, de nombreux kits premium combinent ces puces avec des dissipateurs thermiques de masse plus élevée ou même des barres avec caloducs, non pas pour des raisons esthétiques, mais pour stabiliser les variations thermiques qui altèrent le signal.

Pourquoi SK Hynix domine désormais là où Samsung régnait autrefois

En DDR4, dire « B-die » était synonyme de faibles latences et de mise à l’échelle propre ; les overclockeurs en ont fait une religion. Avec la DDR5, Samsung a perdu ce halo en raison d’une combinaison de processus, de maturité des pilotes et, surtout, de la rapidité avec laquelle SK hynix a peaufiné sa puce M. Si la puce A de deuxième génération se confirme comme étant un silicium qui élève la base à 7 200 et maintient une courbe de tension favorable, SK hynix consolidera un leadership qui, à ce stade, ne semble plus temporaire.

À quoi s’attendre à court terme

Le plus judicieux est d’anticiper des kits 2×24 Go et 2×48 Go à 7 200-7 600 MT/s comme premier lot.avec des PCB 8 couches pour le volume et un prix proche des gammes milieu-haut actuelles. À partir de là, nous verrons des éditions avec 10/12 couches et des profils XMP plus ambitieux pour franchir 8 000 à 8 200 MT/s avec une stabilité sur les cartes Z de nouvelle génération.

L’AKBD A-die n’est pas destiné à battre des records de validation ; vise à faire de 7 200 MT/s le nouveau plancher pour la mémoire grand public haut de gamme. Si vous ajoutez à cette base des kits bien conçus, des PCB avec plus de couches si nécessaire et des micrologiciels matures sur les cartes et les processeurs, le résultat est un écosystème dans lequel la bande passante n’est plus le goulot d’étranglement et la latence efficace est à nouveau le champ de bataille. SK hynix a déjà l’inertie en sa faveur; Si cette puce fait ce que son étiquette suggère, la domination de la DDR5 continuera de s’étendre et l’utilisateur gagnera quelque chose qui est souvent oublié : la prévisibilité. Ouvrez la boîte, montez, chargez XMP et vous avez terminé.